在当今信息技术飞速发展的时代,集成电路(IC)作为现代电子系统的核心,其性能的提升与创新离不开两大关键环节的深度融合:器件物理与芯片设计。它们并非孤立存在,而是通过一座名为“协同研发”的桥梁紧密相连。这座桥梁的构筑与通行效率,直接决定了芯片的最终性能、功耗、成本与上市速度。

一、分立与融合:传统的鸿沟与现实的挑战

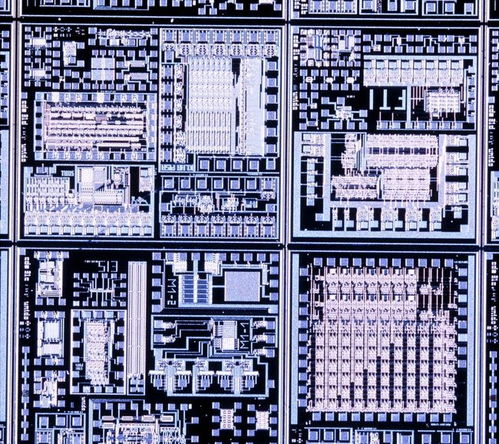

从历史维度看,集成电路的演进长期伴随着器件工艺与电路设计的分工与专业化。器件工程师专注于材料科学、物理机制和制造工艺,致力于在硅片上实现更小、更快、更可靠的晶体管与互连结构。而芯片设计工程师则基于工艺厂商提供的“设计规则”和“器件模型”,利用EDA工具进行逻辑设计、电路仿真和物理实现,以构建复杂的功能系统。

随着工艺节点不断迈向物理极限(如5纳米、3纳米及以下),传统的线性交接模式——即工艺完全定型后,再向设计端提供固定模型——遇到了严峻挑战。先进工艺中复杂的物理效应(如短沟道效应、量子隧穿、工艺波动性剧增等)使得器件行为与理想模型偏差巨大。若设计仅基于滞后的、过于简化的模型,可能导致流片后芯片性能不达预期、功耗超标甚至功能失效,造成巨大的时间和经济成本损失。

二、桥梁的支柱:协同研发的关键要素

因此,构建并强化“器件与设计的桥梁”,实施从早期就开始的协同研发,已成为行业共识。这座桥梁主要由以下几大支柱支撑:

1. 早期设计与工艺协同(DTCO):

在工艺研发的早期阶段,设计团队就介入其中。通过使用工艺开发中的初步器件数据和新结构(如GAA晶体管、纳米片、背面供电网络等),进行电路级和单元库级的仿真与评估。这能快速反馈给工艺团队,指导其优化器件参数和集成方案,使其更贴合实际电路应用的需求,实现“为设计而制造”。

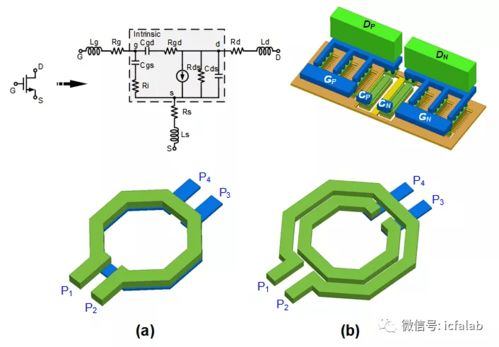

2. 精准的器件建模与PDK:

器件模型的准确性是沟通物理世界与设计世界的“语言”。协同研发要求建模团队与工艺、设计团队紧密合作,开发出能精确反映先进器件在复杂工作条件下(电压、温度、应力、动态开关等)行为的紧凑模型。基于此生成的工艺设计套件(PDK)不再是黑盒,而是蕴含了丰富的物理信息,为设计提供可靠的仿真基础。

3. 系统-技术协同优化(STCO):

这是更宏观层面的桥梁。它要求在定义芯片系统架构(如存算一体、异构集成、新型封装)之初,就综合考虑器件能力、互连技术、封装形式和散热方案。例如,针对AI计算的高带宽需求,协同探索硅光子器件与CMOS电路的集成设计;针对能效瓶颈,共同评估新材料器件(如二维材料、铁电器件)在特定电路模块中的应用潜力。

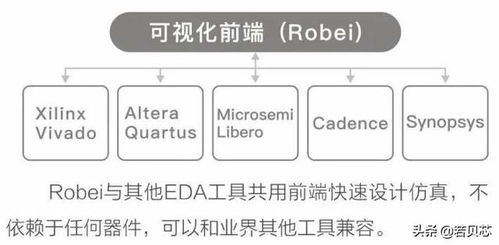

4. 先进的EDA工具与设计方法学:

工具与方法学是工程师过桥的“交通工具”。EDA工具需要深度融合工艺物理信息,支持对制造变异性的统计仿真、对物理效应的电热协同分析等。新的设计方法学,如基于机器学习的模型校准、设计空间探索和自动优化,能够高效处理器件-设计协同产生的海量多维数据,加速最优解的寻找。

三、桥梁的价值:驱动创新与提升竞争力

成功的协同研发能带来多重战略价值:

- 提升产品性能与能效:通过器件特性与电路拓扑的深度匹配,最大化发挥先进工艺的优势,实现PPA(性能、功耗、面积)的同步优化。

- 降低研发风险与成本:早期发现并解决工艺-设计不匹配问题,减少流片迭代次数,显著缩短产品上市周期(Time-to-Market)。

- 激发创新架构:为新器件(如神经形态器件、量子器件)找到最佳电路与系统实现方式,为突破冯·诺依曼瓶颈等根本性问题开辟路径。

- 构筑生态壁垒:对于IDM(垂直整合制造商)或深度绑定的Fab-Fabless生态,强大的协同研发能力是其核心护城河。

###

集成电路的发展史,是一部器件创新与设计创新相互牵引、相互成就的历史。在“后摩尔时代”,单纯依靠工艺微缩已难以为继,“器件与设计的协同研发”这座桥梁的重要性愈发凸显。它要求工程师具备跨领域的知识视野,要求企业建立更开放、更敏捷的合作模式,更要求整个产业生态朝着深度融合的方向演进。唯有如此,才能持续驱动芯片技术的突破,支撑起智能时代万物互联的宏伟蓝图。